USER'S MANUAL

## CHAPTER 13 Z80185/195 INSTRUCTION SET

## **13.1 INTRODUCTION**

This chapter describes the instruction set of the Z80185/195 family processors. To minimize the number of pages required and to eliminate redundant information, instructions that differ only in where the operand(s) reside are described together. After some introductory sections, all instructions are described in alphabetical order, typically in one page per instruction. Each description includes the following parts:

- 3. The header line includes the assembly language mnemonic and operand(s). These items identify the instruction. So that one instruction description can cover many different instructions, operands are often given as an alphabetic code that stands for many possible values. Such codes are listed in the next section.

- 4. The Operation line presents the function of the instruction in a symbolic form.

- 5. The Format section shows how the instruction(s) is (are) structured in memory. For instruction types with more than one kind of operand, separate formats are given for each kind.

- 6. The Description presents the function of the instruction in text form.

7. Timing shows how many bus cycles (M Cycles) and minimum number of clocks (T States) the processor requires to execute the instruction. For instructions with more than one kind of operand, separate timings may be given for each kind.

In this manual, the number of M Cycles reflects only the number of read and write bus cycles that occur during the fetching and execution of the instruction. Internal idle times are not included in the number of M Cycles. The minimum number of T States (clocks) required to execute each instruction are given separately for the Z80 and Z8018x families, each total being followed by a breakdown of the number of clocks required for each M Cycle and internal idle period (the latter are shown as "n idle") in the instruction. As both the Z80185 and Z80195 utilize the Z8S180 core, the Z8018x timings are appropriate. The Z80 timings are included for reference only. In some Z80 T State breakdowns, short internal idle times may not be broken out from the M Cycle which they precede or follow. For I/O instructions of the Z80180x family including the Z80185/195, T States are given separately for registers in the "180 core" (those which are typically addressed 0-3F) and for all other on-chip and off-chip registers, reflecting the fact that the processor automatically inserts one "wait state" in M Cycles for registers in the latter category.

- 8. Condition Bits Affected shows whether and how the instruction affects the Flag register F.

- 9. An example is included for almost all instruction types.

## Zilog

#### **13.2 OPERAND CODES**

- (aa) (mn), (IX+d), (IY+d), or the 8-bit contents of memory at the address in BC, DE, or HL.

- cc a condition code Z, NZ, C, NC, PE, PO, P, or M

- cc' a condition code Z, NZ, C, or NC

- d a signed 8-bit displacement, from an index register or the Program Counter PC

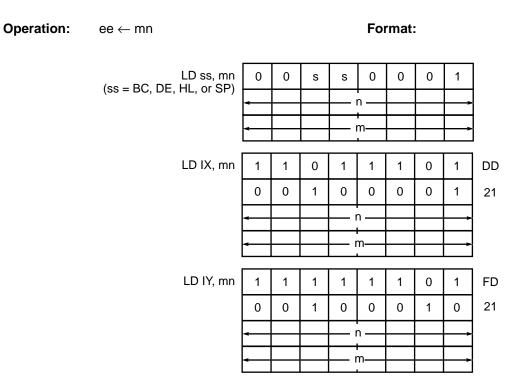

- ee a 16-bit register BC, DE, HL, SP, IX, or IY.

- (IX+d), (IY +D) The 8-bit contents of memory at the address obtained by adding the contents of index register IX or IY and the signed 8-bit displacement d given in the instruction.

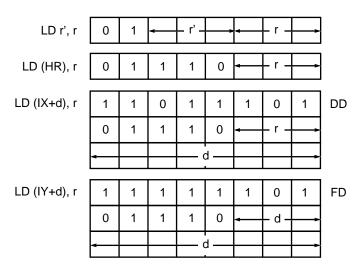

- m r or (HL) or (IX+d) or (IY+d)

- mn a 16-bit "immediate" or "literal" address or value given in the instruction

- (mn) the 8-bit contents of memory at an address given in the instruction

### 13.3 Z80 STATUS INDICATORS (FLAGS)

The flag registers (F and  $F^{l}$ ) supply information to the user regarding the statue of the Z80 at any given time. The bit positions for each flag is shown below:

| 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

|---|---|---|---|---|-----|---|---|

| s | z | х | Ν | Х | P/V | Ν | С |

where:

| С   | = | Carry Flag           |

|-----|---|----------------------|

| Ν   | = | Add/Subtract         |

| P/V | = | Parity/Overflow Flag |

| Н   | = | Half Carry Flag      |

| Ζ   | = | Zero Flag            |

| S   | = | Sign Flag            |

| Х   | = | Not Used             |

Each of the two Z80 Flag Registers contains six bits of statue information which are set or reset by CPU operations. (Bits 3 and 5 are not used.) Four of these bits are testable (C, P/V, Z, and S) for use with conditional Jump, Call, or Return instructions. Two flags are not testable (H, N) and are used for BCD arithmetic.

an 8-bit "immediate" or "literal" value given in the instruction

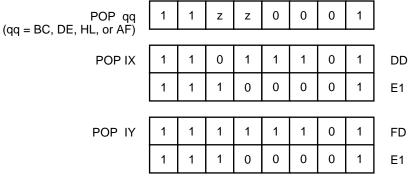

- a 16-bit register BC, DE, HL, IX, IY, or the concatenation of the Accumulator A as the MSbyte and the flags F as the LSbyte

- qq a 16-bit register BC, DE, HL, or the concatenation of the Accumulator A as the MSbyte and the flags F as the LSbyte

- an 8-bit register A, B, C, D, E, H, or L.

- rr a 16-bit register HL, IX, or IY

n

pp

r

tt

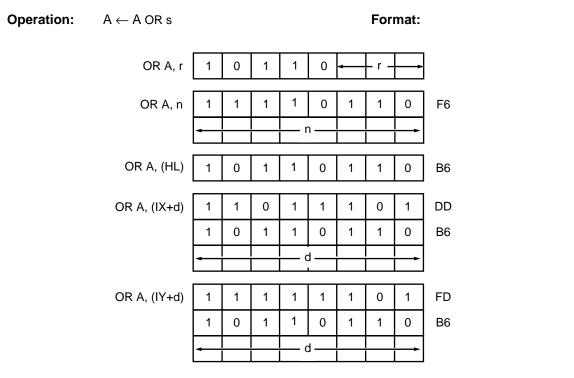

- s r or n or (HL) or (IX+d) or (IY+d)

- ss a 16-bit register BC, DE, HL, or the Stack Pointer SP.

- like ss, except that the encoded value that corresponds to HL in ss means "the destination register HL, IX, or IY".

#### 13.3.1 Carry Flag (C)

The carry bit is set or reset depending on the operation being performed. For 'ADD' instructions that generate a carry and 'SUBTRACT' instructions that generate a borrow, the Carry flag will be set. The Carry flag is reset by an ADD that does not generate a carry and by a 'SUBTRACT' that generates no borrow. This saved carry facilitates software routines for extended precision arithmetic. Also, the 'DAA' instruction will set the Carry flag if the conditions for making the decimal adjustment are met.

For instructions RLA, RRA, RL, and RR, the carry bit is used as a link between the LSB and MSB for any register or memory location. During instructions RLCA, RLC, and SLA, the carry contains the last value shifted out of bit 7 of any register or memory location. During instructions RRCA, RRC, SRA, and SRL the carry contains the last value shifted out of bit 0 of any register or memory location.

For the logical instructions AND, OR, and XOR, the carry will be reset.

The Carry flag can also be set (SCF) and complemented (CCF).

## 13.3.2 Add/Subtract Flag (N)

This flag is used by the decimal adjust accumulator instruction (DAA) to distinguish between 'ADD' and 'SUBTRACT' instructions. For all 'ADD' instructions, N will be set to a '0'. For all 'SUBTRACT' instructions, N will be set to a '1.'

## 13.3.3 Parity/Overflow Flag (P/V)

This flag is set to a particular state depending on the operation being performed.

For arithmetic operations, this flag indicates an overflow condition when the result in the Accumulator is greater than the maximum possible number (+127) or is less than the minimum possible number (-128). This overflow condition can be determined by examining the sign bits of the operands.

For addition, operands with different signs will never cause overflow. When adding operands with like signs and the result has a different sign, the overflow flag is set. For example:

| +120 | = | 0111 | 1000 |       |     |

|------|---|------|------|-------|-----|

| +105 | = | 0110 | 1001 |       |     |

| +225 | = | 1110 | 0001 | (–95) | SUM |

The two numbers added together have resulted in a number that exceeds +127 and the two positive operands has resulted in a negative number (-95) which is incorrect. The Overflow flag is therefore set.

For subtraction, overflow can occur for operands of unlike signs. Operands of like sign will never cause overflow. For example:

| +127    | 0111 | 1111 | MINUEND    |

|---------|------|------|------------|

| (-) -64 | 1100 | 0000 | SUBTRAHEND |

| +191    | 1011 | 1111 | DIFFERENCE |

The minuend sign has changed from a positive to a negative, giving an incorrect difference. Overflow is therefore set.

Another method for predicting an overflow is to observe the carry into and out of the sign bit. If there is a carry in and no carry out, or if there is no carry in and a carry out, then overflow has occurred.

This flag is also used with logical operations and rotate instructions to indicate the parity of the result. The number of '1' bits in a byte are counted. If the total is odd, 'ODD' parity (P=0) is flagged. If the total is even, 'EVEN' parity is flagged (P=1). During search instructions (CPI, CPIR, CPD, CPDR) andblock transfer instructions (LDI, LDIR, LDD, LDDR) the P/V flag monitors the state of the byte count register (BC). When decrementing, if the byte counter results in a zero value, the flag is reset to 0, otherwise the flag is set to1.

During LD A, I and LD A, R instructions, the P/V flag is set with the contents of the interrupt enable flip-flop (IFF2) for storage or testing.

When inputting a byte from an I/O device, IN r, (C), the P/V flag is adjusted to indicate the parity of the data.

## 13.3.4 Half Carry Flag (H)

The Half Carry Flag (H) is set or reset depending on the carry and borrow status between bits 3 and 4 of an 8-bit arithmetic operation. This flag is used by the decimal adjust accumulator instruction (DAA) to correct the result of a packed BCD add or subtract operation. The H flag is set (1) or reset (0) according to the following table:

| Н | Add                                     | Subtract                     |

|---|-----------------------------------------|------------------------------|

| 1 | There is a carry from<br>Bit 3 to Bit 4 | There is a borrow from Bit 4 |

| 0 | There is no carry from Bit 3 to Bit 4   | There is a borrow from Bit 4 |

## 13.3.5 Zero Flag (Z)

The Zero Flag (Z) is set or reset if the result generated by the execution of certain instructions is zero.

For 8-bit arithmetic and logical operations, the Z flag is set to '1' if the resulting byte in the Accumulator is zero. If the byte is not zero, the Z flag is reset to '0'.

For compare (search) instructions, the Z flag is set to '1' if the value in the Accumulator is equal to the value in the memory location pointed to by the contents of the register pair HL.

When testing a bit in a register or memory location, the Z flag contains the complemented state of the indicated bit (see Bit b, s).

When inputting or outputting a byte between a memory location and an I/O device (INI, IND, OUTI, and OUTD), if the result of decrementing the B register is zero, the Z flag is set, otherwise it is reset. Also for byte inputs from I/O devices using IN r, (C), the Z Flag is set to indicate a zero byte input.

## 13.3.6 Sign Flag(S)

The Sign Flag (S) stores the state of the most significant bit of the Accumulator (bit 7). When the Z80 performs arithmetic operations on signed numbers, binary two's complement notation is used to represent and process numeric information. A positive number is identified by a '0' in bit 7. A negative number is identified by a '1.' The binary equivalent of the magnitude of a positive number is stored in bits 0 to 6

## **13.4 THE INSTRUCTION SET**

for a total range of from 0 to 127. A negative number is represented by the two's complement of the equivalent positive number. The total range for negative numbers is from -1 to -128.

When inputting a byte from an I/O device to a register, IN r, (C), the S flag will indicate either positive (S=0) or negative (S=1) data.

#### **Operation:** $A \leftarrow A + s + CY$

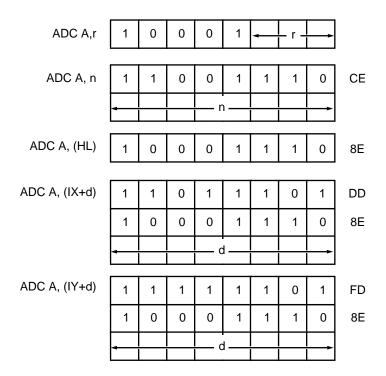

#### Format:

**Description:** The s operand and the Carry Flag ("C" in the F register) are added to the contents of the Accumulator A, the result is stored in A, and the flags are set as described below. "s" can be any of a register r, an "immediate" value n in the instruction itself, a memory location selected by the contents of the HL register pair, or a memory location selected by the sum of the contents of an index register IX or IY and a signed 8-bit displacement d. In the register form, r selects the source register as follows:

# Register

| В | 000 |

|---|-----|

| С | 001 |

| D | 010 |

| Е | 011 |

| Н | 100 |

| L | 101 |

| А | 111 |

r

#### Timing:

| Instruction   | M Cycles | Z80 T States           | Z18x T States          |

|---------------|----------|------------------------|------------------------|

| ADC A, r      | 1        | 4                      | 4 (3+ 1 int)           |

| ADC A, n      | 2        | 7 (4, 3)               | 6 (3, 3)               |

| ADC A, (HL)   | 2        | 7 (4, 3)               | 6 (3, 3)               |

| ADC A, (IX+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

| ADC A, (IY+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

#### **Condition Bits Affected:**

- Z: Set if result is zero; reset otherwise

- H: Set if carry from bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from bit 7; reset otherwise

- **Example:** If the Accumulator contents are 16H, the Carry Flag is set, the HL register pair contains 6666H, and address 6666H contains 10H, after the execution of

ADC A, (HL)

the Accumulator will contain 27H.

## ADC HL, ss

**Operation:**  $HL \leftarrow HL + ss + CY$

#### Format:

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | ED |

|---|---|---|---|---|---|---|---|----|

| 0 | 1 | S | S | 1 | 0 | 1 | 0 |    |

**Description:** The contents of register pair ss (any of register pairs BC, DE, HL, or SP) and the Carry flag (C flag in the F register) are added to the contents of register pair HL, the result is stored in HL, and the C flag reflects whether there was a carry out. Operand ss is specified as follows in the assembled object code:

| Register Pair | SS |

|---------------|----|

| BC            | 00 |

| DE            | 01 |

| HL            | 10 |

| SP            | 11 |

#### Timing:

| M Cycles | Z80 T States     | Z18x T States    |

|----------|------------------|------------------|

| 2        | 15 (4, 4, 7 int) | 10 (3, 3, 4 int) |

#### **Condition Bits Affected:**

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- R: Set if carry out of bit 11; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from bit 15; reset otherwise

#### Example

If the register pair BC contains 2222H, register pair HL contains 5437H and the Carry Flag is set, after the execution of

ADC HL, BC

the contents of HL will be 765AH.

## ADD, A, s

**Operation:**  $A \leftarrow A + s$

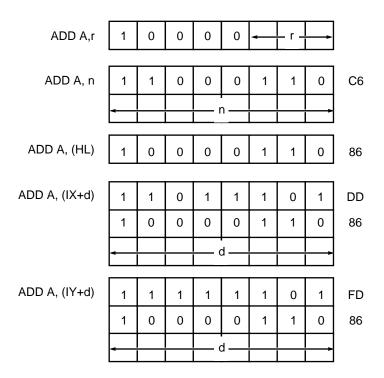

Format:

**Description:** The s operand is added to the value in the Accumulator (A), the result is stored in A, and the flags are set as described below. "s" can be any of a register r, an "immediate" value n in the instruction itself, a memory location selected by the contents of the HL register pair, or a memory location selected by the sum of the contents of an index register IX or IY and a signed 8-bit displacement d. In the register form, r selects a source register as follows:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| Е        | 011 |

| Н        | 100 |

| L        | 101 |

| А        | 111 |

#### :: Timing:

| Instruction  | M Cycles | Z80 T States           | Z18x T States          |

|--------------|----------|------------------------|------------------------|

| ADD A,r      | 1        | 4                      | 4 (3, 1 int)           |

| ADD A,n      | 2        | 7 (4, 3)               | 6 (3, 3)               |

| ADD A,(HL)   | 2        | 7 (4, 3)               | 6 (3, 3)               |

| ADD A,(IX+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

| ADD A,(IY+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

#### **Condition Bits Affected:**

- S: Set if result is negative, reset otherwise

- Z: Set if result is 0; reset otherwise

- H: Set if carry from bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from bit 7; reset otherwise

- **Example:** If the Accumulator (A) contains 11H, the Index Register IY contains 1000H, and memory location 1005H contains 22H, then after the execution of

ADD A, (IY + 5)

A will contain 33H, and the S, Z, H, P/V, and C flags will all be reset.

| Operation: | rr ← rr + tt                                  |   |   |   |   | For | mat: |   |   |    |

|------------|-----------------------------------------------|---|---|---|---|-----|------|---|---|----|

|            | ADD HL, tt<br>(tt = BC, DC, HL, or SP)        | 0 | 0 | t | t | 1   | 0    | 0 | 1 |    |

|            | <b>ADD IX, tt</b><br>(tt = BC, DE, IX, or SP) | 1 | 1 | 0 | 1 | 1   | 1    | 0 | 1 | DD |

|            |                                               | 0 | 0 | t | t | 1   | 0    | 0 | 1 |    |

|            |                                               |   |   |   |   |     |      |   |   |    |

|            | ADD IY, tt<br>(tt = BC, DE, IY, or SP)        | 1 | 1 | 1 | 1 | 1   | 1    | 0 | 1 | FD |

|            | ( = 20, 22, 11, 0. 01)                        |   | 0 | t | t | 1   | 0    | 0 | 1 |    |

**Description:** The contents of 16-bit register tt are added to the contents of 16-bit register rr, the result is stored in rr, and the C flag reflects whether there was a carry out. The destination register "rr" can be register pair HL or an index register IX or

IY. The source register "tt" is encoded as follows:

| Register                   | tt |

|----------------------------|----|

| BC                         | 00 |

| DE                         | 01 |

| same as rr (HL, IX, or IY) | 10 |

| SP                         | 11 |

#### Timing:

| Instruction | M Cycles | Z80 T States     | Z18x T States    |

|-------------|----------|------------------|------------------|

| ADD HL, tt  | 1        | 11 (4, 7 int)    | 7 (3, 4 int)     |

| ADD IX, tt  | 2        | 15 (4, 4, 7 int) | 10 (3, 3, 4 int) |

| ADD IY, tt  | 2        | 15 (4, 4, 7 int) | 10 (3, 3, 4 int) |

#### **Condition Bits Affected:**

- S: Not affected

- Z: Not affected

- H: Set if carry out of bit 11; reset otherwise

- P/V: Not affected

- N: Reset

- C: Set if carry out of bit 15; reset otherwise

**Example:** If BC contains 0102H and IX contains 1234H, then after execution of

ADD IX, BC

IX will contain 1336H.

## AND A, s

| Operation: | $A \gets A \text{ and } s$ |   |   |   |   |        |   | Forr  | nat: |    |

|------------|----------------------------|---|---|---|---|--------|---|-------|------|----|

|            | AND A, r                   | 1 | 0 | 1 | 0 | 0      | - | – r – |      |    |

|            | AND A, n                   | 1 | 1 | 1 | 0 | 0      | 1 | 1     | 0    | E6 |

|            |                            |   |   |   | r | ۱ ——   |   |       |      |    |

|            | AND A, (HL)                | 1 | 0 | 1 | 0 | 0      | 1 | 1     | 0    | A6 |

|            | AND A, (IX+d)              | 1 | 1 | 0 | 1 | 1      | 1 | 0     | 1    | DD |

|            |                            | 1 | 0 | 1 | 0 | 0      | 1 | 1     | 0    | A6 |

|            |                            | - |   |   | ( | d      |   |       |      |    |

|            | AND A, (IY+d)              | 1 | 1 | 1 | 1 | 1      | 1 | 0     | 1    | DD |

|            |                            | 1 | 0 | 1 | 0 | 0      | 1 | 1     | 0    | A6 |

|            |                            | - |   |   |   | d —— t |   |       |      |    |

**Description:** The s operand is logically ANDed with the value in the Accumulator (A), the result is stored in A, and the flags are set as described below. "s" can be any of a register r, an "immediate" value n in the instruction itself, a memory location selected by the contents of the HL register pair, or a memory location selected by the sum of the contents of an index register IX or IY and a signed 8-bit displacement d. In

the register form, r selects a source register as follows:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| А        | 111 |

#### Timing:

| Instruction   | M Cycles | Z80 T States           | Z180x States           |

|---------------|----------|------------------------|------------------------|

| AND A, r      | 1        | 4                      | 4 (3 + 1 int)          |

| AND A, n      | 2        | 7 (4, 3)               | 6 (3, 3)               |

| AND A, (HL)   | 2        | 7 (4, 3)               | 6 (3, 3)               |

| AND A, (IX+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

| AND A, (IX+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

**Condition Bits Affected:**

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set

- P/V: Set if parity even; reset otherwise

- N: Reset

- C: Reset

- **Example:** If the B register contains 7BH and the Accumulator contains C3H after the execution of

AND A,B

the Accumulator will contain 43H.

| Operation:   | $Z  flag \gets NOT  (bit b of m)$                                                                                                                                                                                                                                                                                                                                               |   |   |   |       |   |   | Format: |   |    |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|---|---|---------|---|----|--|

|              | BIT b, r                                                                                                                                                                                                                                                                                                                                                                        | 1 | 1 | 0 | 0     | 1 | 0 | 1       | 1 | СВ |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 0 | 1 | 4 | _ b _ |   | 4 | – r –   |   |    |  |

|              | BIT b, (HL)                                                                                                                                                                                                                                                                                                                                                                     | 1 | 1 | 0 | 0     | 1 | 0 | 1       | 1 | СВ |  |

|              | DIT 0, (ITC)                                                                                                                                                                                                                                                                                                                                                                    | 0 | 1 | • | - b - | - | 1 | 1       | 0 | CD |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   |       |   |   |         | Ū |    |  |

|              | BIT b, (IX+d)                                                                                                                                                                                                                                                                                                                                                                   | 1 | 1 | 0 | 1     | 1 | 1 | 0       | 1 | DD |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 1 | 1 | 0 | 0     | 1 | 0 | 1       | 1 | СВ |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 4 |   |   |       |   |   |         | ► |    |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 0 | 1 | - | b_    | - | 1 | 1       | 0 |    |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   |       |   |   |         |   |    |  |

|              | BIT b, (IY+d)                                                                                                                                                                                                                                                                                                                                                                   | 1 | 1 | 1 | 1     | 1 | 1 | 0       | 1 | FD |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 1 | 1 | 0 | 0     | 1 | 0 | 1       | 1 | СВ |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 4 |   |   |       | t |   |         | ► |    |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                 | 0 | 1 | - | _ b _ | → | 1 | 1       | 0 |    |  |

| Description: | The Z flag is set if bit b of operand m is<br>zero, or cleared if the bit is 1. b can be 0<br>for the LS bit through 7 for the MS bit. "m"<br>can be a register r, a memory location<br>selected by the contents of the HL register<br>pair, or a memory location selected by the<br>sum of the contents of an index register IX<br>or IY and a signed 8-bit displacement d. In |   |   |   |       |   |   |         |   |    |  |

the register form, r selects the register as follows:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| А        | 111 |

## Timing:

| Instruction   | M Cycles | Z80 T States       | Z18x T States      |

|---------------|----------|--------------------|--------------------|

| BIT b, r      | 2        | 8 (4, 4)           | 6 (3, 3)           |

| BIT b, (HL)   | 3        | 12 (4, 4, 4)       | 9 (3, 3, 3)        |

| BIT b, (IX+d) | 5        | 20 (4, 4, 3, 5, 4) | 15 (3, 3, 3, 3, 3) |

| BIT b, (IY+d) | 5        | 20 (4, 4, 3, 5, 4) | 15 (3, 3, 3, 3, 3) |

## **Condition Bits Affected:**

- S: Unknown

- Z: Set if specified bit is 0; reset otherwise

- H: Set

- P/V: Unknown

- N: Reset

- C: Not affected

- **Example:** If IY contains 1000H, and memory location 0FF0H contains BFH, then after the execution of

BIT 6, (IY - 16)

the Z flag will be 1. (For any of the other seven bits in IY-16, the Z flag would be 0.)

Operation:

$\begin{array}{ll} \text{IF cc true:} & (\text{SP-1}) \leftarrow \text{PC}_{\text{H}}, \, \text{SP} \leftarrow \text{SP-2}, \\ & (\text{SP-2}) \leftarrow \text{PC}_{\text{I}}, \, \text{PC} \leftarrow \text{mn} \end{array}$

| 1 | 1 | ┥ | -cc- |        | 1 | 0 | 0 |

|---|---|---|------|--------|---|---|---|

| - |   |   | r    | י<br>י |   |   |   |

|   |   |   | r    | n      |   |   |   |

**Note:** The n value in the assembled object code above is the less significant byte of the 2-byte memory address.

**Description:** If condition cc is true, this instruction pushes the current contents of the Program Counter (PC) onto the top of the stack, then loads the value mn into PC, to point to the address in memory where the first opcode of a subroutine is to be fetched. (At the end of the subroutine, a RETurn instruction can be used to return to the original program flow by popping the top of the stack back into PC.) If condition cc is false, the Program Counter is incremented as usual, and the program continues with the next sequential

instruction. The stack push is accomplished by first decrementing the current contents of the Stack Pointer (SP), loading the high-order byte of the PC contents into the memory address now pointed to by SP; then decrementing SP again, and loading the low-order byte of the PC contents into the top of the stack. Because this is a 3-byte instruction, the Program Counter will have been incremented by three before the push is executed. Condition cc is programmed as one of eight values which correspond to condition bits in the Flag Register (register F). These eight status are defined in the table below:

|              | cc                    | Condition       | Relevant Flag  |                                                                                                                                                                    |   |

|--------------|-----------------------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|              | 000                   | NZ non zero     | Z              |                                                                                                                                                                    |   |

|              | 001                   | Z zero          | Z              |                                                                                                                                                                    |   |

|              | 010                   | NC non carry    | С              |                                                                                                                                                                    |   |

|              | 011                   | C carry         | С              |                                                                                                                                                                    |   |

|              | 100                   | PO parity odd   | P/V            |                                                                                                                                                                    |   |

|              | 101                   | PE parity even  | P/V            |                                                                                                                                                                    |   |

|              | 110                   | P sign positive | S              |                                                                                                                                                                    |   |

|              | 111                   | M sign negative | S              |                                                                                                                                                                    |   |

| Timing:      | If cc is true:        |                 |                |                                                                                                                                                                    |   |

|              | Z80 M Cycles          | Z80 T State     | s Z180x M Cycl | es Z180x T States                                                                                                                                                  |   |

|              | 5                     | 17 (4, 3, 4, 3, | 3) 5           | 16 (3, 3, 3, 1 int, 3, 3)                                                                                                                                          |   |

|              | If cc is false:       |                 |                |                                                                                                                                                                    |   |

|              | Z80 M Cycles          | Z80 T State     | s Z180x M Cycl | es Z180x T States                                                                                                                                                  |   |

|              | 3                     | 10 (4, 3, 3)    | 2              | 6 (3, 3)                                                                                                                                                           |   |

| Condition Bi | ts Affected:<br>None. |                 | Example:       | If the C Flag in the F register is reset, the<br>contents of the Program Counter are<br>1A47H, the contents of the Stack Pointer<br>are 3002H, and the instruction | Э |

#### Format:

#### CALL NC, 2135H

is located in locations 1A47H -1A49H, then after the execution of this instruction, the contents of memory address 3001H will be 1AH, the contents of address 3000H will be 4AH, the contents of the Stack Pointer will be 3000H, and the contents of the Program Counter will be 2135H, pointing to the address of the first opcode of the subroutine now to be executed.

## CALL mn

1

1

0

0

1

1

0

0

CD

Image: Constraint of the second secon

**Note:** The n value in the assembled object code above is the less significant byte of the 2-byte memory address.

**Description:** The current contents of the Program Counter (PC) are pushed onto the top of the stack. The value mn is then loaded into the PC to point to the address in memory where the first opcode of a subroutine is to be fetched. (At the end of the subroutine, a RETurn instruction can be used to return to the original program flow by popping the top of the stack back into the PC.) The push is accomplished by first decrementing the current contents of the Stack Pointer, loading the high-order byte of the PC contents into the memory address now pointed to by the SP; then decrementing SP again, and loading the low-order byte of the PC contents into the top of stack. Because this is a 3-byte instruction, the Program Counter will have been incremented by three before the push is executed.

#### Timing:

| M Cycles | Z80 T States       | Z180x T States            |

|----------|--------------------|---------------------------|

| 5        | 17 (4, 3, 4, 3, 3) | 16 (3, 3, 3, 1 int, 3, 3) |

#### **Condition Bits Affected:**

None.

**Example:** If the contents of the Program Counter are 1A47H, the contents of the Stack Pointer are 3002H, and the instruction

#### CALL 2135H

is located at adddresses 1A47H -1A49H after the execution of this instruction, the contents of memory address 3001H will be 1AH, the contents of address 3000H will be 4AH, the contents of the Stack Pointer will be 3000H, and the contents of the Program Counter will be 2135H, pointing to the address of the first opcode of the subroutine now to be executed.

Format:

## CCF

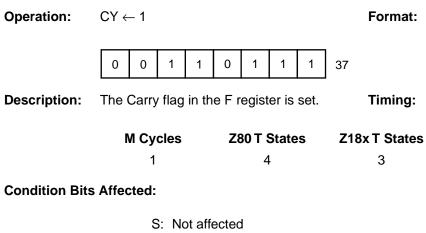

| Operation:                         | CY ←  | - /CY | ,      |       |            |        |         |       |     | Format:    |

|------------------------------------|-------|-------|--------|-------|------------|--------|---------|-------|-----|------------|

|                                    | 0     | 0     | 1      | 1     | 1          | 1      | 1       | 1     | ЗF  |            |

| Description:                       | The C | Carry | flag i | n the | Fre        | gister | r is in | verte | d.  | Timing:    |

|                                    | N     | l Cyc | cles   |       | <b>Z</b> 8 | OT S   | tates   | 5     | Z18 | x T States |

|                                    |       | 1     |        |       |            | 4      |         |       |     | 3          |

| Condition Bits Affected:           |       |       |        |       |            |        |         |       |     |            |

| S: Not affected<br>Z: Not affected |       |       |        |       |            |        |         |       |     |            |

- H: Previous carry will be copied

- P/V: Not affected

- N: Reset

- C: Reset otherwise

| Operation:   | A – s        |      |     |       |       |     |     | Fo    | ormat | :  |

|--------------|--------------|------|-----|-------|-------|-----|-----|-------|-------|----|

|              | CP A,r       | 1    | 0   | 1     | 1     | 1   | 4   | – r – |       |    |

|              | CP A, n      | 1    | 1   | 1     | 1     | 1   | 1   | 1     | 0     | FE |

|              |              | •    |     |       |       | n   |     |       |       |    |

|              | CP A, (HL)   | 1    | 0   | 1     | 1     | 1   | 1   | 1     | 0     | BE |

|              | CP A, (IX+d) | 1    | 1   | 0     | 1     | 1   | 1   | 0     | 1     | DD |

|              |              | 1    | 0   | 1     | 1     | 1   | 1   | 1     | 0     | BE |

|              |              |      |     |       |       | d — |     |       |       |    |

|              | CP A, (IY+d) | 1    | 1   | 1     | 1     | 1   | 1   | 0     | 1     | FD |

|              |              | 1    | 0   | 1     | 1     | 1   | 1   | 1     | 0     | BE |

|              |              | •    |     |       |       | : k |     |       |       |    |

| Description: | The operand  | s is | sub | tract | ed fi | mor | the |       |       |    |

**Description:** The operand s is subtracted from the contents of the Accumulator (A), the result is discarded so that A is not affected, but the result is reflected in the flags, which are set as described below. "s" can be any of a register r, an "immediate" value n in the instruction itself, a memory location selected by the contents of the HL register pair, or a memory location selected by the sum of the contents of an index register IX or IY and a signed 8-bit displacement d. In

the register form, r selectes a source register as follows:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| А        | 111 |

Timing:

| Instruction  | M Cycles | Z80 T States           | Z18x T States          |

|--------------|----------|------------------------|------------------------|

| CP A, r      | 1        | 4                      | 4 (3 + 1 int)          |

| CP A, n      | 2        | 7 (4, 3)               | 6 (3, 3)               |

| CP A, (HL)   | 2        | 7 (4, 3)               | 6 (3, 3)               |

| CP A, (IX+d) | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

| CP A,(IY+d)  | 4        | 19 (4, 4, 3, 5 int, 3) | 14 (3, 3, 3, 2 int, 3) |

**Condition Bits Affected:**

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if borrow from bit 4; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Set

- C: Set if borrow; reset otherwise

- **Example:** If the Accumulator contains 63H, the HL register pair contains 6000H and memory location 6000H contains 60H, the instruction

CP A, (HL)

will result in the the following Flags:

S=0, Z=0, H=0, P/V=0, N=1, C=0

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | ED |

|---|---|---|---|---|---|---|---|----|

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | A9 |

**Description:** The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of equality, the Z flag is set. HL and the Byte Counter

Timing:

| M Cycles | Z80 T States        | Z180x T States      |

|----------|---------------------|---------------------|

| 3        | 16 (4, 4, 3, 5 int) | 12 (3, 3, 3, 3 int) |

#### **Condition Bits Affected:**

- S: Set if A-(HL) is negative; reset otherwise

- Z: Set if A = (HL); reset otherwise

- H: Set if borrow from bit 4; reset otherwise

- P/V: Reset if BC is now 0000; set otherwise

- N: Set

- C: Not Affected:

- **Example:** If the HL register pair contains 1111H, memory location 1111H contains 3BH, the Accumulator contains 3BH, and BC contains 0001H, then after the execution of

#### CPD

BC will contain 0000H, the HL register pair will contain 1110H, the Z flag in the F register will be set, and the P/V flag in the F register will be reset. There will be no effect on the contents of the Accumulator or address 1111H. (register pair BC) are decremented, and

the P/V flag is set to reflect whether BC

has been decremented to zero.

#### Operation: A –(HL), HL $\leftarrow$ HL –1, BC $\leftarrow$ BC –1 Format:

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | ED |

|---|---|---|---|---|---|---|---|----|

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | B9 |

Description: The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of equality, the Z flag is set. The HL and BC (Byte Counter) register pairs are decremented, and the P/V flag is set to reflect whether BC has decremented been to zero. lf decrementing causes the BC to go to zero or if A = (HL), the instruction is terminated.

If BC is not zero and A  $\neq$  (HL), the instruction is repeated. Interrupts will be recognized and refresh cycles may be executed after each data transfer. Note that if BC is set to zero prior to instruction execution, the instruction will loop through 64 Kbytes if no match is found.

Timing: For each repetition with BC  $\neq$  0 and A  $\neq$ (HL):

| M Cycles | Z80 T States         | Z180x T States      |

|----------|----------------------|---------------------|

| 3        | 21 (4, 4, 3, 10 int) | 14 (3, 3, 3, 5 int) |

For BC = 0 or A = (HL):

| M Cycles | Z80 T States        | Z180x T States      |

|----------|---------------------|---------------------|

| 3        | 16 (4, 4, 3, 5 int) | 12 (3, 3, 3, 3 int) |

#### **Condition Bits Affected:**

- S: Set if A-(HL) is negative; reset otherwise

- Z: Set if A = (HL); reset otherwise

- H: Set if borrow from bit 4; reset otherwise

- P/V: Reset if BC is now 0000; set otherwise

- N: Set

- C: Not Affected:

- Example: If the HL register pair contains 1118H, the Accumulator contains F3H. BC contains 0007H, and memory locations have these contents.

(1118H) : 52H (1117H) : 00H (1116H) : F3H

Then after the execution of

#### CPDR

the contents of HL will be 1115H, the contents of BC will be 0004H, and the P/V and Z flags in the F register will both be set.

#### Z80185/195 User's Manual

## CPI

**Operation:** A- (HL), HL  $\leftarrow$  HL +1, BC  $\leftarrow$  BC -1 **Format:**

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | ED |

|---|---|---|---|---|---|---|---|----|

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | A1 |

Description: The contents of the memory location addressed by the HL register are compared with the contents of the Accumulator. In case of equality, the Z flag is set. Then HL is incremented, the Byte Counter (register pair BC) is decremented, and the P/V bit is set to reflect whether BC has been decremented to zero.

| M Cycles | Z80 T States        | Z180x T States      |

|----------|---------------------|---------------------|

| 3        | 16 (4, 4, 3, 5 int) | 12 (3, 3, 3, 3 int) |

#### **Condition Bits Affected:**

- S: Set if A-(HL) is negative; reset otherwise

- Z: Set if A = (HL); reset otherwise

- H: Set if borrow from bit 4; reset otherwise

- P/V: Reset if BC is now 0000; set otherwise

- N: Set

- C: Not affected

- **Example:** If the HL register pair contains 1111H, memory location 1111H contains 3BH, the Accumulator contains 3BH, and BC contains 0001H. Then after the execution of

CPI

BC will contain 0000H, the HL register pair will contain 1112H, the Z flag in the F register will be set, and the P/V flag in the F register will be reset. Neither the Accumulator or memory location 1111H are affected.

| <b>CPIR</b> |  |

|-------------|--|

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | ED |

|---|---|---|---|---|---|---|---|----|

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | B1 |

**Description:** The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of equality, the Z flag is set. HL is incremented and the Byte Counter (register pair BC) is decremented. The P/V flag is set to reflect whether BC has been decremented to zero. If decrementing causes the BC to go to zero or if A = (HL), the instruction is terminated. If BC is not zero and  $A \neq$  (HL), the instruction is repeated. Interrupts will be recognized and refresh cycles may be executed after each data transfer. Note that if BC is set to zero before instruction execution, the instruction will loop through 64 Kbytes if no match is found.

**Timing:** For each repetition with BC  $\neq$  0 and A  $\neq$  (HL):

| M Cycles | Z80 T States            | Z18x T States       |

|----------|-------------------------|---------------------|

| 3        | 21 (4, 4, 3, 5, 10 int) | 14 (3, 3, 3, 5 int) |

For BC = 0 or A = (HL):

| M Cycles | Z80 T States        | Z18x T States       |

|----------|---------------------|---------------------|

| 3        | 16 (4, 4, 3, 5 int) | 12 (3, 3, 3, 3 int) |

#### **Condition Bits Affected:**

- S: Set if A-(HL) is negative; reset otherwise

- Z: Set if A = (HL); reset otherwise

- H: Set if borrow from bit 4; reset otherwise

- P/V: Reset if BC now 0000; set otherwise

- N: Set

- C: Not Affected:

- **Example:** If the HL register pair contains 1111H, the Accumulator contains F3H, BC contains 0007H, and memory locations have these contents:

(1111H) : 52H (1112H) : 00H (1113H) : F3H

Then after the execution of:

CPIR

the contents of register pair HL will be 1114H, BC will contain 0004H, and the P/V and Z flags in the F register will both be set.

## CPL

| Operation:     | $A \gets /A$           |                                     | Format:                 |                                             |

|----------------|------------------------|-------------------------------------|-------------------------|---------------------------------------------|

| Description:   | 0 0 1 0                | 1 1 1 1 1<br>e Accumulator (registe | 2F<br>er <b>Timing:</b> |                                             |

| Description.   |                        | ne's complemented).                 | , innig.                |                                             |

|                | M Cycles               | Z80 T States                        | Z180x T States          |                                             |

|                | 1                      | 4                                   | 3                       |                                             |

| Condition Bits | s Affected:            |                                     | Example:                | If the contents of the Accumulator are D4H: |

|                | S: Not af              |                                     |                         |                                             |

|                | Z: Not af              | fected                              |                         |                                             |

|                | H: Set<br>P/V: Not aff | fected                              |                         |                                             |

|                | N: Set                 |                                     |                         |                                             |

|                | C: Not af              | fected                              |                         |                                             |

|                | 1 0 1 1                | 0 1 0 0                             |                         |                                             |

|                | after the execution    | ı of                                |                         | the Accumulator contents will be 4BH:       |

|                | CPL                    |                                     |                         |                                             |

## DAA

**Operation:** Decimal Adjust Accumulator

Format:

**Description:** This instruction conditionally adjusts the Accumulator after addition and subtraction of BCD values. For addition

(ADD, ADC, INC) or subtraction (SUB, SBC, DEC, NEG), the following table indicates the operation performed:

| Operation | C Before<br>DAA | Hex Value<br>In Upper<br>Digit (bit 7-4) | H Before<br>DAA | Hex Value<br>In Lower<br>Digit (bit 3-0) | Number<br>Added<br>To Byte | C After<br>DAA |

|-----------|-----------------|------------------------------------------|-----------------|------------------------------------------|----------------------------|----------------|

|           | 0               | 9-0                                      | 0               | 0-9                                      | 00                         | 0              |

|           | 0               | 0-8                                      | 0               | A-F                                      | 06                         | 0              |

|           | 0               | 0-9                                      | 1               | 0-3                                      | 06                         | 0              |

| ADD       | 0               | A-F                                      | 0               | 0-9                                      | 60                         | 1              |

| ADC }     | 0               | 9-F                                      | 0               | A-F                                      | 66                         | 1              |

| INC       | 0               | A-F                                      | 1               | 0-3                                      | 66                         | 1              |

|           | 1               | 0-2                                      | 0               | 0-9                                      | 60                         | 1              |

|           | 1               | 0-2                                      | 0               | A-F                                      | 66                         | 1              |

|           | 1               | 0-3                                      | 1               | 0-3                                      | 66                         | 1              |

| SUB       | 0               | 0-9                                      | 0               | 0-9                                      | 00                         | 0              |

| SBC       | 0               | 0-8                                      | 1               | 6-F                                      | FA                         | 0              |

| DEC       | 1               | 7-F                                      | 0               | 0-9                                      | A0                         | 1              |

| NEG       | 1               | 6-7                                      | 1               | 6-F                                      | 9A                         | 1              |

#### Timing:

| M Cycles | Z80 T States | Z18x T States |

|----------|--------------|---------------|

| 1        | 4            | 4 (3 + 1 int) |

## Condition Bits Affected:

- S: Set if most significant bit of the Accumulator is 1 after operation; reset otherwise

- Z: Set if the Accumulator is zero after operation; reset otherwise

- H: See instruction

- P/V: Set if the Accumulator has even parity after operation; reset otherwise

- N: Not affected

- C: See description

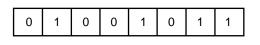

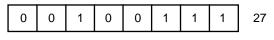

**Example:** If 15 (BCD) and 27 (BCD) are added, decimal arithmetic gives this result:

\_\_\_\_\_

But when the binary representations are added in the Accumulator according to standard binary arithmetic,

| 0001   | 0101 |      |

|--------|------|------|

| + 0010 | 0111 |      |

| 0011   | 1100 | = 3C |

The DAA instruction adjusts this result so that the correct BCD representation is obtained:

| 0011   | 1100 |      |

|--------|------|------|

| + 0000 | 0110 |      |

| 0100   | 0010 | = 42 |

## DEC ee

| Operation: | $ee \leftarrow ee - 1$             |   |   |   |   | For | mat: |   |   |    |

|------------|------------------------------------|---|---|---|---|-----|------|---|---|----|

|            | DEC ss<br>(ss = BC, DE, HL, or SP) | 0 | 0 | S | S | 1   | 0    | 1 | 1 |    |

|            | DEC IX                             | 1 | 1 | 0 | 1 | 1   | 1    | 0 | 1 | DD |

|            |                                    | 0 | 0 | 1 | 0 | 1   | 0    | 1 | 1 | 2B |

|            |                                    |   |   |   |   |     |      |   |   | 1  |

|            | DEC IY                             | 1 | 1 | 1 | 1 | 1   | 1    | 0 | 1 | FD |

|            |                                    | 0 | 0 | 1 | 0 | 1   | 0    | 1 | 1 | 2B |

|            |                                    |   |   |   |   |     |      |   |   |    |

**Description:** 16-bit register ee is decremented by 1. The flags are not affected. "ee" can be any of the register pairs BC, DE, or HL, the Stack Pointer SP, or an index register IX or IY. In the first form shown above, "ss" is encoded as follows:

| Register | SS |

|----------|----|

| BC       | 00 |

| DE       | 01 |

| HL       | 10 |

| SP       | 11 |

#### Timing:

| Instruction | M Cycles | Z80 T States     | Z18x T States   |

|-------------|----------|------------------|-----------------|

| DEC ss      | 1        | 6 (4, 2 int)     | 4 (3, 1 int)    |

| DEC IX      | 2        | 10 (4, 4, 2 int) | 7 (3, 3, 1 int) |

| DEC IY      | 2        | 10 (4, 4, 2 int) | 7 (3, 3, 1 int) |

#### **Condition Bits Affected:**

None

**Example:** If BC contains 0 and the C flag is 0, then after the execution of

DEC BC

BC will contain FFFFH, and the C flag will still be 0.

| Operation: | $m \gets m - 1$ |   |   |   |       |     |   | F | Form | at: |

|------------|-----------------|---|---|---|-------|-----|---|---|------|-----|

|            | DEC r           | 0 | 0 |   | _ r _ |     | 1 | 0 | 1    |     |

|            | DEC (HL)        | 0 | 0 | 1 | 1     | 0   | 1 | 0 | 0    | 35  |

|            | DEC (IX+d)      | 1 | 1 | 0 | 1     | 1   | 1 | 0 | 1    | DD  |

|            |                 | 0 | 0 | 1 | 1     | 0   | 1 | 0 | 0    | 35  |

|            |                 |   |   |   | (     | d   |   |   |      |     |

|            | DEC (IY+d)      | 1 | 1 | 1 | 1     | 1   | 1 | 0 | 1    | FD  |

|            |                 | 0 | 0 | 1 | 1     | 0   | 1 | 0 | 1    | 35  |

|            |                 | • |   |   | (     | d — |   |   |      |     |

**Description:** The 8-bit value in the m operand is decremented by one, and the flags (except C) are set as described below. "m" can be a register r, a memory location selected by the contents of the HL register pair, or a memory location selected by the sum of the contents of an index register IX or IY and a signed 8-bit displacement d. In

the register form, r selects the register as follows:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| А        | 111 |

#### Timing:

| Instruction | M Cycles | Z80 T States              | Z18x T States                    |

|-------------|----------|---------------------------|----------------------------------|

| DEC r       | 1        | 4                         | 4 (3 + 1 int)                    |

| DEC (HL)    | 3        | 11 (4, 4, 3)              | 10 (3, 3, 1 int, 3)              |

| DEC (IX+d)  | 5        | 23 (4, 4, 3, 5 int, 4, 3) | 18 (3, 3, 3, 2 int, 3, 1 int, 3) |

| DEC (IY+d)  | 5        | 23 (4, 4, 3, 5 int, 4, 3) | 18 (3, 3, 3, 2 int, 3, 1 int, 3) |

#### **Condition Bits Affected:**

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if borrow from bit 4, reset otherwise

- P/V: Set if 80H to 7FH; reset otherwise

- N: Set

- C: Not affected

**Example:** If the D register contains byte 2AH, after the execution of

DEC D

register D will contain 29H.

## DI

| Operation:    | $IFF \gets 0$                         |                        | Format:        |                                                        |

|---------------|---------------------------------------|------------------------|----------------|--------------------------------------------------------|

|               | 1 1 1 1                               | 0 0 1 1                | F3             |                                                        |

| Description:  | DI disables mas<br>resetting the inte | skable interrupts      | -              | disables the maskable interrupts during its execution. |

|               | (IFF1 and IFF2). N                    |                        | ction          |                                                        |

|               |                                       |                        | Timing:        |                                                        |

|               | M Cycles                              | Z80 T States           | Z180x T States |                                                        |

|               | 1                                     | 4                      | 3              |                                                        |

| Condition Bit | s Affected:<br>None.                  |                        |                |                                                        |

| Example:      | When the CPU exe                      | ecutes the instruction | on             |                                                        |

|               | DI                                    |                        |                |                                                        |

|               |                                       |                        |                |                                                        |

the maskable interrupt is disabled until it is subsequently re-enabled by an EI instruction. The CPU will not respond to an Interrupt Request (INT) signal until that time.

DJNZ, d

| Operation:    | Decrement and Jump if Non-Zero                                                                                                                            |                                                          | Format:                                                                                                                           |                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|               | 0 0 0 1                                                                                                                                                   |                                                          | 10                                                                                                                                |                                                                                                                                        |

| Description:  | This instruction i<br>conditional jump inst<br>register value is<br>branching. The B reg                                                                  | ructions except the used to determ                       | nine                                                                                                                              | -126 to +129 bytes. The assembler<br>automatically adjusts for the twice<br>incremented PC.                                            |

|               | and if a non zero valu<br>of the displacement<br>Program Counter<br>instruction is fetche                                                                 | ue remains, the va<br>d is added to<br>(PC). The n       | alue<br>the<br>next                                                                                                               | If decrementing leaves B with a zero value, the next instruction to be executed is taken from the location following this instruction. |

|               | designated by the ne<br>The jump is measure<br>the instruction opcoc                                                                                      | d from the addres                                        | s of Timing:                                                                                                                      | if B ≠ 0:                                                                                                                              |

|               | M Cycles                                                                                                                                                  | Z80 T States                                             | Z18x T States                                                                                                                     | 6                                                                                                                                      |

|               | 2                                                                                                                                                         | 13 (5 ,3, 5 int)                                         | ) 9 (3, 1 int, 3, 2 i                                                                                                             | nt)                                                                                                                                    |

|               | If B = 0:                                                                                                                                                 |                                                          |                                                                                                                                   |                                                                                                                                        |

|               | M Cycles                                                                                                                                                  | Z80 T States                                             | Z18x T States                                                                                                                     | 6                                                                                                                                      |

|               | 2                                                                                                                                                         | 8 (5 ,3)                                                 | 7 (3, 1 int, 3)                                                                                                                   |                                                                                                                                        |

| Condition Bit | s Affected:                                                                                                                                               |                                                          |                                                                                                                                   | instruction. This routine moves a line from                                                                                            |

|               | None.                                                                                                                                                     |                                                          |                                                                                                                                   | an input buffer (INBUF) to an output buffer                                                                                            |

| Example:      | A typical software routine is used to(OUTBUF). It moves the bytes unta CR, or until it has moved 80demonstrate the use of the DJNZwhichever occurs first. |                                                          |                                                                                                                                   |                                                                                                                                        |

|               | LD<br>LD<br>LD                                                                                                                                            | B, 80<br>HL, Inbuf<br>DE, Outbuf                         | ;Set up counter<br>;Set up pointers                                                                                               |                                                                                                                                        |

|               | LOOP: LD<br>LD<br>CP<br>JR<br>INC<br>INC<br>DJNZ                                                                                                          | A, (HL)<br>(DE), A<br>ODH<br>Z, DONE<br>HL<br>DE<br>LOOP | ;Get next byte from in<br>;Store in output buffe<br>;Is it a CR?<br>;Yes finished<br>;Increment pointers<br>;Loop back if 80 byte |                                                                                                                                        |

|               | DONE:                                                                                                                                                     |                                                          |                                                                                                                                   |                                                                                                                                        |

ΕI

| Operation:     | $IFF \leftarrow 1$                                              |                                                                                                                        | Format:                     |                                                                |

|----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------|

|                | 1 1 1 1                                                         | 1 0 1 1                                                                                                                | FB                          |                                                                |

| Description:   | interrupt enable flip<br>to '1' allowing<br>maskable interrupt. | ot instruction sets both<br>flops (IFFI and IFF2)<br>recognition of any<br>Note that during the<br>instruction and the | )<br>/<br>e <b>Timing</b> : | following instruction, maskable interrupts not yet be enabled. |

|                | M Cycles                                                        | Z80 T States                                                                                                           | Z18x T States               |                                                                |

|                | 1                                                               | 4                                                                                                                      | 3                           |                                                                |

| Condition Bits | s Affected:<br>None.                                            |                                                                                                                        |                             |                                                                |

| Example:       | When the CPU exe                                                | cutes instruction                                                                                                      |                             |                                                                |

|                | EI<br>RETI                                                      |                                                                                                                        |                             |                                                                |

|                |                                                                 | rrupt will be enabled of the RETI instruction                                                                          |                             |                                                                |

UM971800200

## EX AF, AF'

| Operation:                       | $AF \leftrightarrow AF'$                                                                                                                  | Format:      |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

|                                  | 0 0 0 0 1 0 0 08                                                                                                                          | 3            |  |  |  |  |

| Description:                     | The 2-byte contents of the register pairs AF and AF' are exchanged. (Note: register pair AF <sup>1</sup> consists of registers A' and F') | Timing:      |  |  |  |  |

|                                  | M Cycles Z80 T States Z18                                                                                                                 | 8x T States  |  |  |  |  |

|                                  | 1 4 4                                                                                                                                     | 4 (3, 1 int) |  |  |  |  |

| Condition Bits Affected:<br>All. |                                                                                                                                           |              |  |  |  |  |

| Example:                         | If the content of register pair AF is 9900H,<br>and the content of register pair AF <sup>1</sup> is<br>5944H, after the instruction       |              |  |  |  |  |

|                                  | EX AF, AF'                                                                                                                                |              |  |  |  |  |

|                                  | the contents of AF will be 5944H, and the contents of AF' will be 9900H.                                                                  |              |  |  |  |  |

| Operation:     | $DE \leftrightarrow HL$                                                                                                | Format:    |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

|                | 1 1 1 0 1 0 1 1 EB                                                                                                     | 5          |  |  |  |

| Description:   | The 2-byte contents of register pairs DE<br>and HL are exchanged. No flags are<br>affected.                            | Timing:    |  |  |  |

|                | M Cycles Z80 T States Z18                                                                                              | x T States |  |  |  |

|                | 1 4                                                                                                                    | 3          |  |  |  |

| Condition Bits | Affected:<br>None.                                                                                                     |            |  |  |  |

| Example:       | If the content of register pair DE is 2822H,<br>and the content of register pair HL is<br>499AH, after the instruction |            |  |  |  |

|                | EX DE, HL                                                                                                              |            |  |  |  |

the content of register pair DE will be 499AH and the content of register pair HL will be 2822H.

Zilog

# EX (SP), rr

| Operation: | $rr_{L} \leftrightarrow (SP),  rr_{H} \leftrightarrow (SP+1)$ |   |   |   |   | Format: |   |   |   |    |

|------------|---------------------------------------------------------------|---|---|---|---|---------|---|---|---|----|

|            | EX (SP), HL                                                   | 1 | 1 | 1 | 0 | 0       | 0 | 1 | 1 | E3 |

|            | EX (SP), IX                                                   | 1 | 1 | 0 | 1 | 1       | 1 | 0 | 1 | DD |

|            |                                                               | 1 | 1 | 1 | 0 | 0       | 0 | 1 | 1 | E3 |

|            |                                                               |   |   |   |   |         |   |   |   | 1  |